(19) INDIA

(22) Date of filing of Application :05/12/2013 (43) Publication Date : 24/06/2016

## (54) Title of the invention: MEMORY SHARING IN GRAPHICS PROCESSING UNIT

| (51) International classification      | :G06F9/48,G06F9/50 | (71)Name of Applicant:                                          |

|----------------------------------------|--------------------|-----------------------------------------------------------------|

| (31) Priority Document No              | :13/164615         | 1)QUALCOMM Incorporated                                         |

| (32) Priority Date                     | :20/06/2011        | Address of Applicant :5775 Morehouse Drive ATTN:                |

| (33) Name of priority country          | :U.S.A.            | International IP Administration San Diego California 92121 1714 |

| (86) International Application No      | :PCT/US2012/038659 | U.S.A.                                                          |

| Filing Date                            | :18/05/2012        | (72)Name of Inventor:                                           |

| (87) International Publication No      | :WO 2012/177343    | 1)ARVO Jukka Pekka                                              |

| (61) Patent of Addition to Application | :NA                |                                                                 |

| Number                                 | :NA                |                                                                 |

| Filing Date                            | .IVA               |                                                                 |

| (62) Divisional to Application Number  | :NA                |                                                                 |

| Filing Date                            | :NA                |                                                                 |

## (57) Abstract:

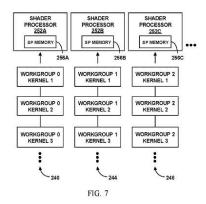

Aspects of this disclosure are directed to a method of processing data with a graphics processing unit (GPU). According to some aspects of the disclosure the method comprises receiving input defining execution orders for a shader processor wherein the execution orders comprise plurality of kernel designations and a plurality of workgroup designations. The method may also include assigning workgroups of kernels identified in the plurality of workgroup designations and the plurality of kernel designations to the shader processor. The method may also include executing by the shader processor the workgroups of kernels identified in the plurality of workgroup designations and the plurality of kernel designations to process input data wherein executing the stream of execution orders comprises sharing input data between two or more workgroups identified in the plurality of workgroup designations.

No. of Pages: 42 No. of Claims: 29